آموزش فلیپ فلاپ

فلیپ فلاپ (Flip-Flop) یکی از بنیادیترین بلوکهای ساختمانی در طراحی سیستمهای دیجیتال است. این المان منطقی وظیفه ذخیرهسازی یک بیت داده باینری (0 یا 1) را بر عهده دارد و به دلیل خاصیت حافظهای خود، در دسته مدارهای ترتیبی (Sequential Circuits) قرار میگیرد. در دوره آموزش الکترونیک بصورت کاربردی و عملی به این موضوع میپردازیم.

آموزش فلیپ فلاپ (Flip-Flop) در مدارهای دیجیتال

در مدارهای ترکیبی (Combinational Circuits) خروجی فقط به ورودیهای لحظهای وابسته است، اما در مدارهای ترتیبی مانند فلیپ فلاپ، خروجی علاوه بر ورودی فعلی، به وضعیت قبلی (Previous State) نیز وابسته خواهد بود. این ویژگی امکان پیادهسازی حافظهها، شمارندهها، رجیسترها و ماشینهای حالت محدود (FSM) را فراهم میکند.

فلیپ فلاپ و اهمیت کلاک در عملکرد آن

فلیپ فلاپها بر اساس سیگنال کلاک (Clock Signal) عمل میکنند. سیگنال کلاک یک موج متناوب است که مرجع زمانی مدار را تعیین میکند. فلیپ فلاپها معمولاً به صورت لبه حساس (Edge Triggered) طراحی میشوند، یعنی تغییر وضعیت آنها تنها در لحظه لبه بالارونده (Rising Edge) یا لبه پایینرونده (Falling Edge) کلاک اتفاق میافتد.

تفاوت اصلی فلیپ فلاپ با لچ (Latch) نیز همین است:

-

لچ (Level Sensitive): خروجی در طول فعال بودن سطح سیگنال تغییر میکند.

-

فلیپ فلاپ (Edge Triggered): تغییر وضعیت فقط در لحظه تغییر لبه کلاک انجام میشود.

این ویژگی سبب پایداری بیشتر فلیپ فلاپ در مدارهای همزمان شده و آن را به عنصر اصلی در طراحی پردازندهها و حافظههای همزمان تبدیل کرده است.

|

|

انواع فلیپ فلاپ در مدارهای دیجیتال

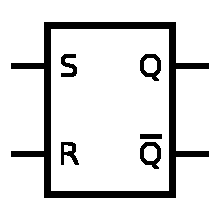

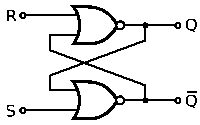

فلیپ فلاپ SR (Set-Reset Flip-Flop)

-

اولین و سادهترین نوع فلیپ فلاپ

-

دارای دو ورودی: S (Set) و R (Reset)

-

در حالت S=1 مقدار خروجی Q برابر 1 میشود.

-

در حالت R=1 مقدار خروجی Q برابر 0 خواهد بود.

-

وقتی هر دو ورودی S=R=1 باشند، حالت مدار نامعین (Invalid) است.

کاربرد: بیشتر جنبه آموزشی دارد و در عمل به دلیل داشتن حالت نامعتبر، کمتر به تنهایی استفاده میشود.

فلیپ فلاپ D (Data or Delay Flip-Flop)

-

پرکاربردترین نوع فلیپ فلاپ

-

تنها یک ورودی دارد که با نام D (Data) مشخص میشود.

-

در لبه فعال کلاک، مقدار ورودی D در خروجی Q ذخیره میشود.

-

حالت نامعین ندارد و بسیار پایدار است.

کاربرد:

-

طراحی رجیسترها برای ذخیره داده

-

حافظههای RAM و Cache

-

بافرهای انتقال داده

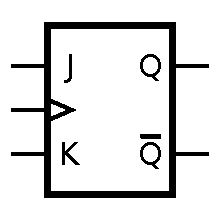

فلیپ فلاپ JK

-

نسخه تکاملیافته فلیپ فلاپ SR

-

دارای دو ورودی J و K است.

-

وقتی J=K=1 باشد، خروجی در هر پالس کلاک تغییر وضعیت (Toggle) میدهد.

-

برخلاف SR هیچ حالت نامعینی ندارد.

کاربرد:

-

طراحی شمارندههای همزمان و ناهمزمان

-

پیادهسازی ماشینهای حالت

-

استفاده در مدارات کنترلی

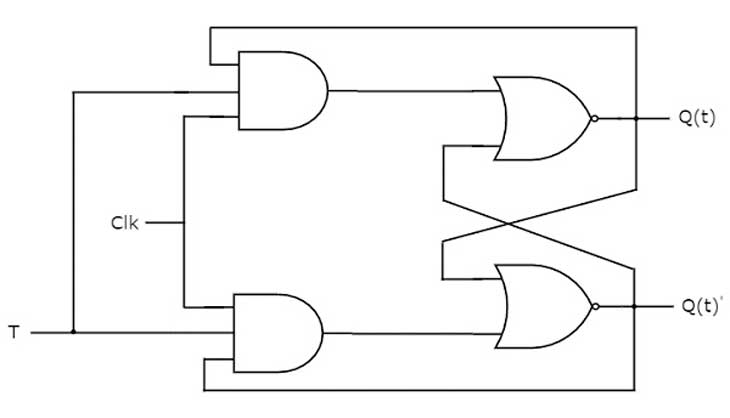

فلیپ فلاپ T (Toggle Flip-Flop)

-

در واقع یک فلیپ فلاپ JK است که ورودیهای J و K آن به هم متصل شدهاند.

-

تنها یک ورودی T دارد.

-

اگر T=1 باشد، در هر پالس کلاک خروجی Q معکوس میشود.

-

اگر T=0 باشد، خروجی ثابت باقی میماند.

کاربرد:

-

اساس طراحی شمارندههای باینری (Binary Counters)

-

مدارهای تقسیمکننده فرکانس

جدول درستی (Truth Table) فلیپ فلاپها

برای تحلیل دقیق عملکرد فلیپ فلاپها از جدول درستی استفاده میشود. به طور خلاصه:

-

فلیپ فلاپ D: خروجی Q برابر مقدار D در لبه کلاک است.

-

فلیپ فلاپ JK: بسته به ورودیها میتواند Set، Reset یا Toggle کند.

-

فلیپ فلاپ T: تنها بین حالت ثابت و Toggle تغییر میکند.

این جدولها به مهندسان کمک میکنند تا رفتار مدار را در شرایط مختلف پیشبینی کنند.

دیاگرام زمانی (Timing Diagram) در فلیپ فلاپها

یکی از نکات پیشرفته در آموزش فلیپ فلاپ، بررسی دیاگرام زمانی (Timing Diagram) است. این دیاگرام نشان میدهد که چگونه ورودیها (D, J, K, T) و سیگنال کلاک بر روی خروجی Q در طول زمان تأثیر میگذارند.

پارامترهای مهم در این تحلیل:

Setup Time (tSU): حداقل زمانی که ورودی باید قبل از لبه فعال کلاک پایدار باشد.

Hold Time (tH): حداقل زمانی که ورودی باید بعد از لبه فعال کلاک پایدار بماند.

Propagation Delay (tPD): تأخیر زمانی بین تغییر ورودی و تغییر خروجی.

این پارامترها در طراحی سیستمهای پرسرعت (High-Speed Digital Systems) مانند پردازندهها و FPGA اهمیت حیاتی دارند.

کاربردهای عملی فلیپ فلاپها

فلیپ فلاپها به دلیل قابلیت ذخیرهسازی و تغییر وضعیت، کاربردهای گستردهای در مدارهای دیجیتال دارند:

-

ذخیره یک بیت داده بهعنوان کوچکترین واحد حافظه

-

طراحی رجیسترها برای ذخیره و انتقال داده در CPU

-

شمارندهها در سیستمهای کنترلی و پردازشی

-

ماشینهای حالت محدود (FSM) در طراحی سختافزارهای دیجیتال

-

سینکسازی سیگنالها در سیستمهای همزمان

-

حافظههای دیجیتال مانند RAM و ROM

فلیپ فلاپها هسته اصلی طراحی دیجیتال محسوب میشوند. آشنایی با انواع فلیپ فلاپ (SR، D، JK و T) و درک تفاوتهای عملکردی آنها، پایهای برای درک مباحث پیچیدهتر مانند طراحی پردازندهها، واحد کنترل، حافظههای دیجیتال و سیستمهای VLSI است. در کلاس آموزش الکترونیک و تعمیرات برد بصورت کاربردی تر این موضوع را بررسی میکنیم.

برای مهندسان و دانشجویان رشته برق و کامپیوتر، یادگیری دقیق مفاهیمی چون جدول درستی، دیاگرام زمانی و محدودیتهای زمانی (Setup & Hold Time) بسیار ضروری است تا بتوانند مدارهای دیجیتال پایدار و پرسرعت طراحی کنند.

سوالات متداول آموزش فلیپ فلاپ

چرا فلیپ فلاپها در طراحی مدارهای همزمان (Synchronous Circuits) ضروری هستند؟

فلیپ فلاپها عناصر اصلی مدارهای دیجیتال همزمان هستند که امکان ذخیرهسازی دادهها و همگامسازی دقیق سیگنالها را فراهم میکنند. حساسیت این المانها به لبه کلاک (Edge Triggered) باعث میشود تغییرات خروجی تنها در لحظه دقیق فعال شدن کلاک رخ دهد. بدون فلیپ فلاپ، مدارهای همزمان ممکن است دچار Race Condition یا Hazard شوند که میتواند منجر به ناپایداری عملکرد در پردازندهها، رجیسترها و شمارندهها شود. استفاده از فلیپ فلاپها تضمین میکند که دادهها به صورت پایدار و قابل پیشبینی بین بلوکهای مختلف سیستم دیجیتال منتقل شوند.

تفاوت عملکرد فلیپ فلاپ D و فلیپ فلاپ JK چیست؟

فلیپ فلاپ D یک مدار حافظه ساده (Single-Bit Storage Element) است که تنها یک ورودی D دارد و مقدار ورودی در لبه فعال کلاک به خروجی منتقل میشود. این فلیپ فلاپ به دلیل حذف حالت نامعین (Elimination of Invalid States) بسیار پایدار است و در رجیسترها و حافظههای دیجیتال کاربرد گسترده دارد.

در مقابل، فلیپ فلاپ JK دارای دو ورودی J و K است. اگر J=K=1 باشد، خروجی Q در هر پالس کلاک تغییر وضعیت میدهد (Toggle Mode). فلیپ فلاپ JK برای طراحی شمارندهها و ماشینهای حالت محدود (FSM) مناسب است و برخلاف SR، هیچ حالت نامعینی ندارد.

Setup Time و Hold Time در فلیپ فلاپها چه مفهومی دارند و چرا اهمیت دارند؟

Setup Time (tSU): حداقل مدت زمانی که ورودی فلیپ فلاپ باید قبل از لبه فعال کلاک ثابت بماند تا تغییر وضعیت صحیح انجام شود.

Hold Time (tH): حداقل زمانی که ورودی باید بعد از لبه فعال کلاک پایدار باقی بماند.

عدم رعایت این مقادیر میتواند باعث وقوع Meta-Stability شود؛ وضعیتی که خروجی فلیپ فلاپ ناپایدار شده و منجر به خطا در سیستمهای دیجیتال پرسرعت میشود. در طراحی پردازندهها، FPGA و مدارهای منطقی همزمان، توجه دقیق به زمانبندی Setup و Hold برای اطمینان از عملکرد صحیح مدار حیاتی است.

چرا فلیپ فلاپ T برای طراحی شمارندههای باینری مناسب است؟

فلیپ فلاپ T با ویژگی Toggle در هر لبه فعال کلاک، رفتار شمارندههای باینری را شبیهسازی میکند. در این فلیپ فلاپ، اگر ورودی T=1 باشد، خروجی Q معکوس میشود و اگر T=0 باشد، خروجی ثابت باقی میماند. ترکیب چند فلیپ فلاپ T در کنار هم امکان طراحی شمارندههای Mod-N، تقسیمکننده فرکانس و ثانیهشمارها را فراهم میکند. به دلیل سادگی و رفتار پیشبینیپذیر، فلیپ فلاپ T یکی از المانهای کلیدی در طراحی سیستمهای دیجیتال زمانبندیشده و شمارندههای همزمان است.

نقش فلیپ فلاپها در معماری پردازنده (CPU) چیست؟

در پردازندهها، فلیپ فلاپها به عنوان حافظههای موقت (Registers) برای ذخیره دادهها، آدرسها و دستورالعملها عمل میکنند. همچنین در واحد کنترل (Control Unit) و Pipeline نقش کلیدی در همگامسازی سیگنالها و جلوگیری از تداخل دادهها دارند. بدون فلیپ فلاپها، اجرای همزمان و پایدار دستورالعملها در CPU امکانپذیر نخواهد بود. علاوه بر این، فلیپ فلاپها پایه طراحی حافظههای Cache، شمارندههای برنامه و بلوکهای FSM هستند که عملکرد پردازنده را بهینه و قابل اعتماد میکنند.